## V - I and I - V Converter:

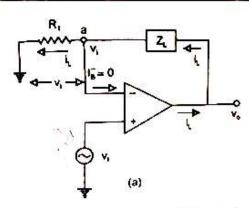

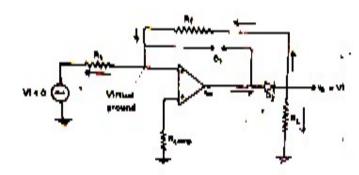

Draw the circuit of a Voltage to Current converter with a Floating load. Explain the operation.

Here, the load  $Z_t$  is floating. Voltage at node 'a' is  $V_t$  because of virtual short( $v_d = 0$ ).

$$V_1 = i_1 R_1$$

but

$$i_i = i_1$$

since  $I_B = 0$ .

Therefore, Eqn (1) can be written as

$$I_L = \frac{v_e}{R_1}$$

That is the input voltage  $v_i$  is converted into an output current of  $v_i/R_1$ .

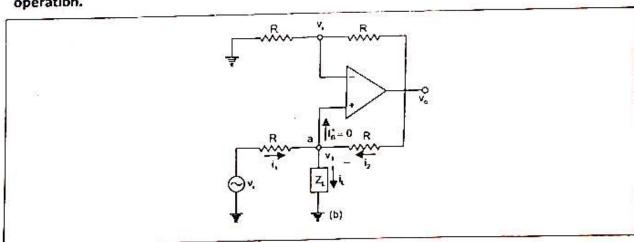

Draw the circuit of a Voltage to Current converter with a Grounded load. Explain the operation.

Here, the load  $Z_i$  is grounded. Let  $v_i$  be the voltage at node 'a'.

Writing KVL, we get

$$i_1 + i_2 = i_L$$

$$\frac{v_i - v_1}{R} + \frac{v_o - v_1}{R} = i_L$$

or

$$v_i + v_o - 2v_1 = i_L R$$

$$v_1 = \frac{v_i + v_o - i_L R}{2}$$

Since the op-amp is used in non-inverting mode, the voltage gain of the non-inverting amplifier circuit is

$$A_{\mathbf{v}} = \frac{v_o}{v_1} = 1 + \frac{R}{R} = 2$$

or

$$v_o = 2v_1 = 2\frac{v_t + v_o - i_L R}{2}$$

or

$$v_o = v_t + v_o - i_L R \text{ or}$$

$$v_t = i_L R \text{ or}$$

$$i_L = \frac{v_t}{R}$$

That is the input voltage  $v_i$  is converted into an output current of  $v_i/R_1$ .

### Applications:

- i) Low voltage dc and ac voltmeter

- ii) LED Tester

- iii) Zener Diode Tester.

# **Op-amp circuits using Diodes:**

### Rectifiers:

Discuss the advantages of a precision rectifier over an ordinary rectifier.

Rectifiers are implemented using non-linear devices such as diodes. The major limitation of ordinary diode is that it cannot rectify voltages below V<sub>r</sub> (~0.7 V). The non-zero forward voltage drop V<sub>r</sub> of a practical diode may cause intolerable errors in low level signal rectification. This shortcoming is avoided by placing the diode inside the negative feedback path of an op-amp. With this, the forward voltage drop can be eliminated to give precision rectification. Hence op-amp rectifiers are called precision rectifiers or small signal rectifiers.

The advantages of precision rectifiers over simple diode rectifiers are as follows:

- 1. No diode voltage drop between input and output

- 2. The ability to rectify very small voltages (<0.7V)

- 3. Amplification if required

- 4. Low output impedance.

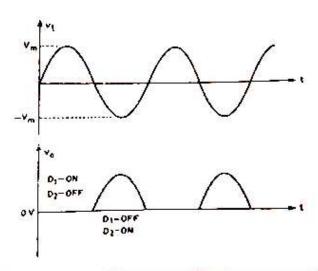

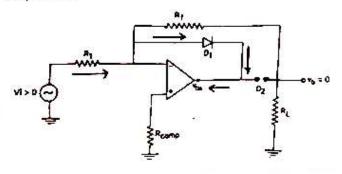

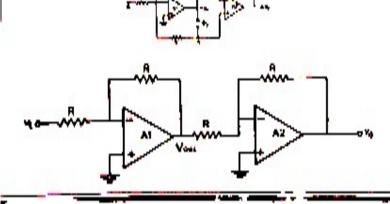

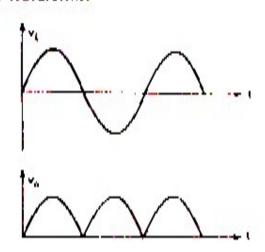

Sketch the circuit of a precision Half Wave Rectifier. Draw the input and output waveforms and explain the circuit operation.

# Circuit diagram:

The precision HWR uses an inverting amplifier configuration.

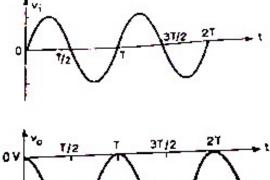

I/O Waveforms:

For, Vi > 0

During the positive half cycle of the input, the opamp output terminal  $V_{OA}$  goes negative, causing  $D_2$  to be reverse biased and  $D_1$  to be forward biased. The op-amp's output voltage  $V_{OA}$  goes negative by one diode drop. Without  $D_1$  in the circuit, the opamp output would be driven to  $-V_{Sal}$ . The purpose of  $D_1$  is to keep the op-amp output from going into saturation. The output voltage is zero.

$$v_o = 0$$

and  $v_{OA} = -0.7V$

During the negative half cycle of the input, the opamp output terminal  $V_{\rm OA}$  goes positive, causing  $D_1$ to be reverse blased and  $D_2$  to be forward blased. While  $D_2$  is forward blased, the circuit functions as an inverting amplifier circuit to give an output

$$V_{ii} = -\frac{R_f}{R_i}(-V_i)$$

With  $R_f = R_i$ , the circuit acts like an inverter.

Thus, the positive half cycle is clipped off and the negative half cycle of the input is inverted.

If  $R_f > R_f$ , the output is an amplified version of the input.

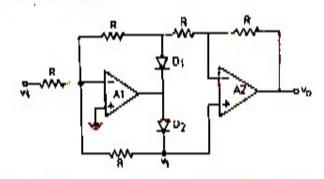

Sketch the circuit of a precision full Wave Rectifier. Draw the input and output waveforms and explain the circuit operation.

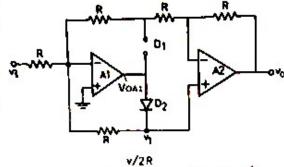

### Circuit diagram:

A precision full wave rectifier is also known as an Absolute value circuit. This means the circuit output is the absolute value of the input peak voltage regardless of the input polarity.

For, V | > 0

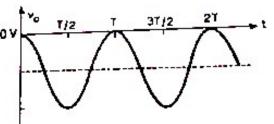

# I/O Waveforms:

During the positive half cycle of the Input, the op-amp A, output terminal V<sub>OA</sub>, goes negative, causing D, to be reverse biased and D, to be forward biased, Both the op-amps A, and A, act as inverter as shown in equivalent circuit.

$$egin{array}{ccc} oldsymbol{v}_{ii} & oldsymbol{v}_{ii} & oldsymbol{v}_{cM1} & oldsymbol{v}_{cM1} & oldsymbol{v}_{ij} \ oldsymbol{v}_{ii} & oldsymbol{v}_{i} \end{array}$$

Fig a

Fig b

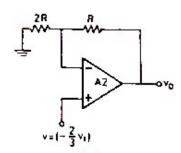

During the negative half cycle of the input, the opamp  $A_1$  output terminal  $V_{OA1}$  goes positive, causing  $D_1$  to be reverse biased and  $D_2$  to be forward biased. The equivalent circuit is shown in Fig a.

Let the output voltage of op-amp  $A_1$  be 'v'. Because of virtual short ( $v_d=0$ ) at op-amp  $A_2$ , the inverting input terminal of op-amp  $A_2$  is also at voltage 'v'.

Applying KCL at node 'a' gives

$$\frac{v_t}{R} + \frac{v}{2R} + \frac{v}{R} = 0 \text{ or }$$

$$v = -\frac{2}{3}v_t$$

But  $v_i < 0$

Therefore,

$$v = -\frac{2}{3}(-v_r)$$

$$v = \frac{2}{3}v_r - \cdots (1)$$

The equivalent circuit of Fig a is a non-inverting amplifier as shown in Fig b.

The output voltage vois

$$v_n = \left(1 + \frac{R}{2R}\right)v$$

$$v_n = \left(1 + \frac{1}{2}\right)\left(\frac{2}{3}v_i\right)$$

$$v_n = \left(\frac{3}{2}\right)\left(\frac{2}{3}v_i\right)$$

$$v_n = v_i$$

# Sample and Hold Circuit:

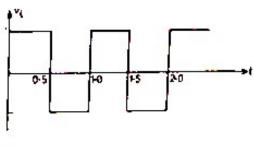

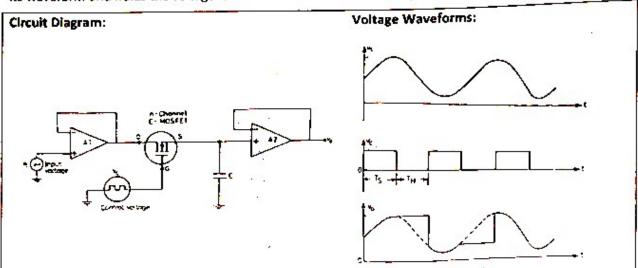

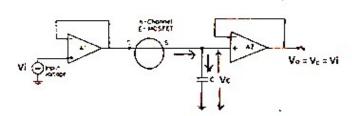

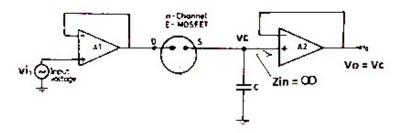

Sketch the op-amp Sample and Hold circuit, draw the Signal, Control and Output voltage waveforms and explain the circuit operation.

A sample and hold circuit samples instantaneous amplitudes of an analog signal voltage at any point in its waveform and holds the voltage level constant until the next sample is acquired.

### Operation:

The n-channel E - MOSFET switch is included to alternately connect and disconnect the capacitor at the output of op-amp  $A_t$ . The analog signal  $V_t$  to be sampled is applied to the drain of E-MOSFET. The MOSFET switch is repeatedly switched ON and OFF by the pulse waveform called the control voltage  $V_t$ . The control voltage  $V_t$  is applied to the gate of E-MOSE.

The frequency of the control voltage  $V_c$  should  $m_c$  kept higher than (at least twice) the input so as to retrieve the input from output waveform.

$$|f_i| \ge 2f_i$$

### When v, is positive:

When the control voltage  $v_c$  is positive, the E-MOSFET turns ON and the capacitor C charges to the instantaneous value of input  $v_c$  with a time constant

$$[R_o + r_{DS}(on)]C$$

# where R<sub>a</sub> is the output resistance of the Voltage follower A<sub>1</sub> and

ros(on) is the resistance of the MOSFET when ON

Thus the input voltage  $v_i$  appears across the capacitor C and then at the output through the voltage follower  $A_2$ .

$$V_{\alpha} = V_{C} = V_{\alpha}$$

When ve is zero:

During the time when control voltage  $v_c$  is zero, the E-MOSFET is OFF. The capacitor C is now facing the high input impedance of the voltage follower  $A_2$  and hence cannot discharge. The capacitor holds the voltage across it.

$$V_o = V_C$$

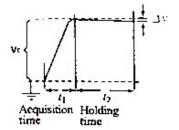

Acquisition time  $t_1$ : The time period  $t_1$ , during which voltage across the capacitor is equal to input voltage is called acquisition time or sample period.

Holding time  $t_2$ : The time period  $t_2$  of  $v_c$  during which the voltage across the capacitor is held constant is called holding time or hold period.

### Differentiator:

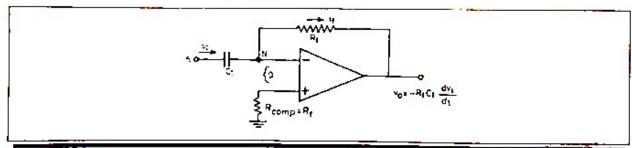

Draw the circuit diagram of basic Op-amp Differentiator. Derive an equation for the output voltage.

Differentiator circuit performs the mathematical operation of differentiation, that is, the output waveform is the derivative of input waveform.

The node N is at virtual ground potential i.e.,  $v_N = 0$ . The current  $i_C$  through the capacitor is

$$i_C = C_1 \frac{d}{dt} (v_t - v_N) = C_1 \frac{d}{dt} (v_t - 0) = C_1 \frac{dv_t}{dt}$$

The current is through the feedback resistor is

$$I_f = \frac{v_N - v_o}{R_f} = \frac{0 - v_o}{R_f} = -\frac{v_o}{R_f}$$

Therefore, the nodal equation at node N is,

$$i_C = i_f + i_{B-}$$

$$i_C = i_f$$

since  $i_{\theta_0} = 0$

$$C_1 \frac{dv_t}{dt} = -\frac{v_o}{R_t}$$

$$v_{ij} = -R_f C_1 \frac{dv_i}{dt}$$

Thus, the output voltage  $v_o$  is a constant  $(-R_fC_t)$  times the derivative of the input voltage  $v_o$ ,  $R_fC_t$  is the time constant of the differentiator. The minus sign indicates a  $180^\circ$  phase shift of the output waveform  $v_o$  with respect to the input signal  $v_o$ .

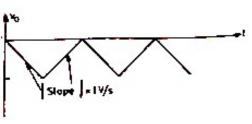

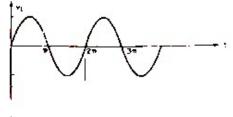

I/O Waveforms:

### Integrator:

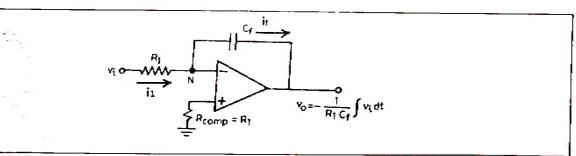

Draw the circuit diagram of basic Op-amp Integrator. Derive an equation for the output voltage.

Integrator circuit performs the mathematical operation of integration, that is, the output waveform is the integration of input waveform.

The node N is at virtual ground potential i.e.,  $v_N = 0$ . The current  $i_f$  through the capacitor  $C_f$  is

$$i_f = C_f \frac{d}{dt} (v_N - v_o) = C_f \frac{d}{dt} (0 - v_o) = -C_f \frac{dv_o}{dt}$$

The current if through the resistor R<sub>1</sub> is

$$i_1 = \frac{v_i}{R_i}$$

Therefore, the nodal equation at node N is,

$$i_{1} = i_{f} + i_{R-}$$

$$i_{1} = i_{f} \quad \text{since } i_{B} = 0$$

$$\frac{v_{i}}{R_{1}} = -C_{f} \frac{dv_{o}}{dt}$$

$$\frac{dv_{o}}{dt} = -\frac{1}{R_{1}C_{f}}v_{i}$$

Integrating both sides, we get

$$\int_{0}^{t} dv_{o} = -\frac{1}{R_{1}C_{f}} \int_{0}^{t} v_{t} dt$$

$$v_{o}(t) = -\frac{1}{R_{1}C_{f}} \int_{0}^{t} v_{s}(t) dt + v_{o}(0)$$

where  $v_o(0)$  is the initial output voltage

Thus, the output voltage  $v_o$  is a constant  $(-1/R_1C_f)$  times the integral of the input voltage  $v_o$ ,  $R_1C_f$  is the time constant of the integrator. The minus sign indicates a  $180^\circ$  phase shift of the output waveform  $v_o$  with respect to the input signal  $v_o$ .

For good integration, one must ensure that the time period T of the input signal is smaller than or equal to  $R_iC_f$ .

$T \leq R_1 C_f$

!/O Waveforms: